ElLATTICEXP2 FAMILIAes una serie de FPGA de bajo costo, tercera generación, no volátiles. Basado en la arquitectura flexiflash única, combina 4 - tela FPGA basada en la tabla de vista de entrada (LUT) con celdas flash no volátiles. Esta arquitectura permite instantáneos (en solo 1 ms), integración de un solo chip y ofrece características como alta relación de E/S de lógica, memoria integrada y distribuida, e I/OS de alto rendimiento flexible y de alto rendimiento. Los dispositivos LATTICEXP2 admiten la tecnología de actualización en vivo con TransFR, que permite actualizaciones de configuración lógica durante la operación del sistema. También presentan 128 - Cifrado de bits de bits de bits y tecnologías de arranque duales para una mayor seguridad y confiabilidad. Con densidades que van desde 5k a 40k LUT, estos FPGA pueden cumplir con varios requisitos de diseño. La familia viene con bloques SYSDSP de alto rendimiento, hasta 4 SysClock PLLS y búferes de E/S versátiles que admiten múltiples estándares. La herramienta de diseño de redes Isplever, junto con los módulos IP pre -diseñados, ayuda a los diseñadores a implementar diseños complejos de manera eficiente. El kit de desarrollo de Brevia proporciona una plataforma conveniente para la evaluación y el diseño, lo que hace que la familia LatticeXP2 sea adecuada para una amplia gama de aplicaciones.

Características de la familia LatTiceXP2

La familia LatticeXP2es una serie de FPGA con múltiples características avanzadas, lo que lo hace adecuado para varias aplicaciones. Aquí están sus características clave:

- arquitectura flexiflash

- Integración instantánea, encendida y única: Logra instantáneamente en 1 ms y permite la integración de un solo chip, lo cual es conveniente para el diseño del sistema y reduce la complejidad del circuito general.

- Relación de alta lógica a - E/S: Ofrece una alta relación, lo que permite una utilización eficiente de los recursos lógicos al tiempo que maneja una cantidad relativamente grande de señales de entrada/salida.

- Memoria incrustada y distribuida: Proporciona memoria integrada y distribuida. El Sysmem EBR integrado puede alcanzar hasta 885 KBITS, y la RAM distribuida puede alcanzar hasta 83 KBIT, cumpliendo diferentes requisitos de almacenamiento de datos en diseños.

- I/OS de alto rendimiento flexible, alto: Los estándares versátiles de soporte de I/OS como DDR/DDR2 y 7: 1 LVDS, y el búfer SYSIO admite múltiples niveles de voltaje como LVCMOS, SSTL, HSTL, PCI, LVD, etc., asegurando la compatibilidad con varios dispositivos externos.

- Tecnología de actualización en vivo

- Tecnología TransFR: Permite actualizaciones de configuración lógica mientras el equipo aún está funcionando, lo que permite actualizaciones sin problemas del sistema sin la necesidad de tiempo de inactividad del sistema.

- Arranque dual con flash SPI externo: Mejora la confiabilidad del sistema. En caso de un problema con una imagen de arranque, el sistema aún puede arrancar desde el otro, asegurando la operación continua.

- Actualizaciones seguras con 128 - Cifrado BitStream de AES de bits: Asegura la seguridad de los datos de diseño durante las actualizaciones. Un algoritmo de cifrado AES de 128 bits y una llave específica de diseño almacenada en - Chip Flash Protege el flujo de bits de que se modifique.

- Arquitectura FPGA optimizada

- Opciones de densidad: Disponible con densidades que van desde 5k a 40k 4 - Tablas de entrada de entrada (LUT), adecuadas para diseños con diferentes requisitos de complejidad, de simple a complejo.

- Recursos de memoria: Además de la memoria mencionada anteriormente, ofrece una gran cantidad de RAM de bloque y RAM distribuida, lo cual es beneficioso para aplicaciones intensivas de datos.

- Embalaje de bajo costo: Viene en opciones de envasado TQFP, PQFP y BGA de bajo costo, reduciendo el costo general del diseño mientras mantiene el rendimiento.

- Bloque SYSDSP de alto rendimiento

- Múltiples bloques y multiplicadores: Equipado con tres a ocho bloques con funciones multiplicadas y de acumulación, y contiene 12 a 32 multiplicadores de 18x18. Cada bloque también admite diferentes configuraciones de multiplicadores como un multiplicador 36x36, cuatro multiplicadores de 18x18 o ocho multiplicadores 9x9, proporcionando flexibilidad para las tareas de procesamiento de señales digitales.

- Interfaces síncronas de fuente pre -ingeniería

- Interfaces de alta velocidad: Las interfaces DDR/DDR2 pueden alcanzar hasta 200MHz/400Mbps, la interfaz LVDS 7: 1 puede alcanzar hasta 600Mbps, y la interfaz genérica puede alcanzar hasta 750 Mbps, lo que permite una transferencia de datos rápidos en aplicaciones como la comunicación de datos de alta velocidad y el procesamiento de video.

- Sistema - Soporte de nivel

- Interfaces de programación y prueba: Cuenta con interfaces SPI/JTAG para la programación de dispositivos y cumple con IEEE Standard 1149.1 escaneo límite para fáciles de prueba y depuración.

- On - Board Oscillator: Se proporciona un oscilador de placa en la placa para el uso de inicialización y propósito general, reduciendo la necesidad de componentes externos.

- Lógica de detección de errores suaves (SED): La lógica SED integrada ayuda a detectar errores suaves, mejorando la confiabilidad del sistema en presencia de interferencia externa.

- Fuente de alimentación: Funciona con un voltaje de núcleo de suministro de alimentación de 1.2V, que es adecuado para diseños de consumo de baja potencia

Arquitectura de la familia LatTiceXP2

- Ventajas del núcleo de la arquitectura Flexiflash: La arquitectura Flexiflash única combina de manera innovadora la tela FPGA basada en tablas de búsqueda de 4 entradas (LUT) con celdas flash no volátiles. Esta arquitectura permite una instantánea rápida de 1 ms y admite la integración de un solo chip, mejorando la compacidad y la confiabilidad del sistema. Mientras tanto, tiene una alta relación lógica-I/O, que puede manejar eficientemente una gran cantidad de operaciones lógicas y tareas de transferencia de datos. La arquitectura también proporciona memoria distribuida e integrada. La RAM de bloque integrada de Sysmem (EBR) puede alcanzar hasta 885 KBIT, y la RAM distribuida puede ser de hasta 83 KBIT, cumpliendo con diferentes requisitos de almacenamiento y procesamiento de datos.

- Trabajo colaborativo de abundantes módulos funcionales

- Módulos SYSDSP de alto rendimiento: Estos módulos contienen 3 a 8 bloques con funciones multiplicadas y acumuladas y 12 - 32 multiplicadores 18x18. Cada bloque también admite múltiples configuraciones de multiplicadores, como un multiplicador 36x36, cuatro multiplicadores de 18x18 o ocho multiplicadores 9x9. Se desempeñan con sobra en el procesamiento de señales digitales y pueden aplicarse ampliamente en campos como el procesamiento de imágenes y audio.

- módulos SYSCLOCK PLL: Cada dispositivo está equipado con hasta 4 bucles bloqueados de fase analógica (PLL), que pueden lograr la multiplicación del reloj, división y funciones de cambio de fase. Proporcionan señales de reloj estables y precisas para el sistema, asegurando el funcionamiento sincrónico y eficiente de cada módulo.

- Buffers de Sysio flexibles: Los tampones SYSIO admiten múltiples niveles de voltaje, como LVCMOS 3.3/2.5/1.8/1.5/1.2, LVTTL, SSTL, HSTL, PCI, LVD, etc., lo que permite una buena compatibilidad con varios dispositivos externos y cumpliendo con diferentes requisitos de interfaz.

- Interfaces sincrónicas de fuente pregustente: Estas interfaces admiten interfaces DDR / DDR2 con una frecuencia máxima de 200MHz y una tasa de transferencia de datos de 400Mbps. La interfaz LVDS 7: 1 tiene una tasa máxima de 600Mbps, y la interfaz genérica puede alcanzar 750Mbps, asegurando la transmisión de datos de alta velocidad y ser adecuada para aplicaciones con altos requisitos de ancho de banda, como la transmisión de video.

- Soporte completo a nivel de sistema: Tiene interfaces SPI/JTAG para la programación y depuración de dispositivos, se ajusta al estándar IEEE Standard 1149.1 de escaneo límite, que es conveniente para las pruebas del sistema. El oscilador en el chip se usa para la inicialización y los fines generales, lo que reduce la dependencia de las fuentes de reloj externas. Además, la lógica de detección de errores suaves (SED) está integrada para mejorar la estabilidad del sistema. El voltaje de la fuente de alimentación operativa es de 1.2V, lo que ayuda a lograr un diseño de consumo de baja potencia.

Aplicaciones de la familia LatTiceXP2

ElSerie LatticeXP2, con sus ricas características, tiene una amplia gama de aplicaciones en múltiples campos:

Campo de procesamiento de video: su interfaz LVDS 7: 1 de alta velocidad permite la transmisión rápida de datos de imagen, lo que lo hace adecuado para aplicaciones de video. Por ejemplo, en los sistemas de videovigilancia de alta definición, puede transmitir eficientemente una gran cantidad de datos de imagen recopilados por cámaras, asegurando la suavidad y el rendimiento en tiempo real de los videos. En los dispositivos de visualización de video, puede transmitir rápidamente las señales de video procesadas al panel de visualización, lo que respalda la visualización de videos de alta resolución y alta tasa de marco.

Campo de control industrial: esta serie tiene la característica de inicio instantáneo (1MS), que es crucial para la respuesta rápida de la lógica de control clave en los sistemas de control industrial. Por ejemplo, en el sistema de control de una línea de producción automatizada, puede iniciarse rápidamente y monitorear y controlar el estado del equipo en tiempo real, mejorando la eficiencia de producción y la estabilidad del sistema. Además, admite buffers de Sysio flexibles con estándares de nivel múltiple e interfaces sincrónicas de origen prediseñadas, lo que hace que sea conveniente conectarse con varios sensores industriales, actuadores y otros dispositivos, cumpliendo con los complejos requisitos de comunicación de los sitios industriales.

Campo de comunicación: admite interfaces DDR/DDR2, con una frecuencia máxima de hasta 200MHz y una tasa de transmisión de datos de 400Mbps, y la tasa de interfaz general puede alcanzar 750 Mbps. Se puede aplicar a los enlaces de procesamiento y transmisión de datos en dispositivos de comunicación. Por ejemplo, en los interruptores de red, los enrutadores y otros dispositivos, puede procesar eficientemente una gran cantidad de paquetes de datos, asegurando la alta velocidad y la estabilidad de la comunicación de la red. Al mismo tiempo, los recursos integrados en chip, como el módulo SYSDSP y PLL, se pueden utilizar para el procesamiento de señales y la gestión del reloj, mejorando el rendimiento de los dispositivos de comunicación.

Campo de sistema integrado: el procesador Soft Lattice32 ™ Soft permite que el LatticeXP2 se use como microcontrolador, proporcionando más opciones para el desarrollo de sistemas integrados. Combinando sus ricos recursos de procesamiento lógico y de señal, así como interfaces de E/S flexibles, en dispositivos integrados como casas inteligentes y medidores de electricidad inteligentes, puede implementar funciones de control complejas y tareas de procesamiento de datos. Además, con la ventaja de la integración de un solo chip, reduce el tamaño y el costo de los dispositivos.

Campo de Internet de las cosas (IoT): el LatticeXP2 admite la tecnología de actualización en vivo, que puede actualizar la configuración lógica mientras el dispositivo se ejecuta, facilitando la actualización remota y la optimización de funciones de los dispositivos IoT. Mientras tanto, la tecnología de cifrado AES de 128 bits garantiza la seguridad de la transmisión y el almacenamiento de datos, que cumple con los estrictos requisitos de seguridad de los dispositivos IoT. En los nodos sensores de IoT, su consumo de baja potencia y sus características de tamaño pequeño se pueden utilizar para lograr una operación a largo plazo y una recopilación, procesamiento y transmisión de datos eficientes.

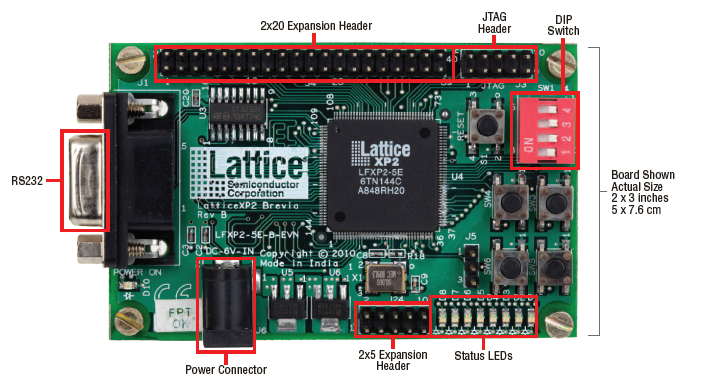

Kit de desarrollo de Brevia

Descripción general del kit

El kit de desarrollo de Brevia es una plataforma fácil de usar y de bajo costo para evaluar y diseñar con FPGA LatticeXP2. Proporciona a los desarrolladores un conjunto completo de recursos, con el objetivo de acelerar el proceso de desarrollo y reducir los costos de desarrollo.

Componentes principales

Ventajas del kit

El kit permite a los desarrolladores evaluar rápidamente el rendimiento y las funciones del FPGA LatticeXP2 con una inversión de bajo costo. Con la ayuda de herramientas de diseño gratuito, diseños de referencia ricos y demostraciones de SOC preparadas, los desarrolladores no necesitan construir funciones básicas desde cero. En cambio, pueden centrarse en las partes únicas de sus diseños, mejorando la eficiencia del desarrollo y acelerando el mercado de productos.

Productos de kit de desarrollo de Brevia

LFXP2-5E-B2-EVN LFXP2-17E-L-EVN LFXP2-17E-H-EVN LFXP2-8E-7TN144C LFXP2-5E-B-EVN

Hoja de datos de la familia LatticeXP2

Dispositivos familiares LatTiceXP2

Lfxp2-5e-6qn208i LFXP2-30E-6FT256I Lfxp2-5e-6qn208c LFXP2-30E-6FTN256I LFXP2-30E-5F672I LFXP2-8E-6FT256I

LFXP2-5E-5M132I LFXP2-17E-5QN208C LFXP2-30E-5FN672C LFXP2-8E-7M132C LFXP2-40E-5F484I LFXP2-5E-6M132C

LFXP2-40E-5F672C LFXP2-8E-6MN132I LFXP2-40E-5FN672I LFXP2-40E-5FN484C LFXP2-5E-5MN132I LFXP2-40E-5FN484I

LFXP2-17E-6FT256C LFXP2-40E-5F672I LFXP2-17E-6F484C LFXP2-5E-6M132I LFXP2-30E-5FT256C LFXP2-40E-6F484I

LFXP2-17E-7FT256C LFXP2-17E-5FTN256I LFXP2-17E-6FN484C LFXP2-17E-5F484C LFXP2-17E-5F484I LFXP2-5E-7FTN256C

LFXP2-40E-6FN484I LFXP2-5E-7MN132C LFXP2-8E-6FTN256I LFXP2-40E-5F484C LFXP2-8E-6TN144C LFXP2-5E-6FT256C

LFXP2-5E-7FT256C LFXP2-8E-6FT256C LFXP2-40E-6FN672I LFXP2-5E-6TN144I LFXP2-17E-7QN208C LFXP2-5E-5M132C

LFXP2-5E-5FTN256I LFXP2-8E-5QN208I LFXP2-5E-5QN208C LFXP2-40E-6FN672C LFXP2-5E-5QN208I LFXP2-30E-5FN484I

LFXP2-17E-7F484C LFXP2-8E-5MN132I LFXP2-17E-6QN208C LFXP2-17E-7FTN256C LFXP2-30E-5F484C LFXP2-30E-6FTN256C

LFXP2-8E-6TN144I LFXP2-17E-5FN484I LFXP2-5E-5TN144I LFXP2-17E-6FT256I LFXP2-8E-7FT256C LFXP2-30E-5FN484C

LFXP2-8E-6M132I LFXP2-5E-6MN132I LFXP2-30E-6FN672C LFXP2-30E-5FT256I LFXP2-30E-6F484I LFXP2-5E-6TN144C

Lista de deseos (0 elementos)

Lista de deseos (0 elementos)